Tak. Nasze moduły są w pełni zgodne ze standardem Sinara i bezproblemowo współpracują z rozwiązaniami innych producentów.

Ekosystem Sinara/ARTIQ dla technologii kwantowych

Te same wyzwania, te same potrzeby – wiele elastycznych rozwiązań: poznaj modułowy system Sinara.

Zbuduj dokładnie taki system, jakiego potrzebujesz

Podczas projektowania układu kontrolno-pomiarowego często napotykanym problemem jest dobranie elektroniki pod konkretne zastosowanie. Często zdarza się, że duża skrzynia (rack) wykorzystywana jest tylko częściowo, a braki w układzie pomiarowym uzupełnia się prowizorycznymi, nierzadko kosztownymi rozwiązaniami. Właśnie dlatego Sinara zyskuje coraz większą popularność na całym świecie i podbija kolejne laboratoria badawcze.

Siła FPGA, prostota Pythona

Moduły Sinara to karty elektroniczne w standardzie EEM (Eurocard Extension Module). Każda z nich posiada opracowany gateware wspierany przez dopasowany software ARTIQ. Dzięki temu wykorzystujesz pełen potencjał FPGA (znacznie szybszy od mikrokontrolerów), równocześnie programując eksperyment prosto ze skryptu pisanego w języku Python.

Od sygnału do systemu

Karty Sinara zaprojektowaliśmy tak, aby oferowały proste funkcjonalności przy zachowaniu najwyższych parametrów. Dzięki temu – niezależnie od tego, czy kontrolujesz 5 czy 1000 kubitów – możesz łatwo rozbudowywać swój system: dodajesz kolejne karty i sterujesz eksperymentem z poziomu „master”, zarządzając podrzędnymi „satelitami”.

Sinara to hardware na otwartej licencji, dzięki czemu każdy użytkownik ma realny wpływ na jego rozwój. Dziś Sinara jest wizytówką międzynarodowej społeczności ion-trap.

Oferujemy:

- moduły Sinara,

- szkolenia z wdrożenia Sinary i konsultacje (od jednogodzinnych do kilkudniowych szkoleń),

- zintegrowane systemy (plug-and-play) z gotowym skryptem do obsługi eksperymentu.

Dlaczego Sinara?

- Modularna architektura umożliwiająca szybkie i elastyczne tworzenie systemów

- Precyzyjne sterowanie sygnałem o niskim szumie i niskim jitterze

- Skrypt pisany w Python

- Hardware na FPGA

- Łatwe i tanie skalowanie przez dokładanie kolejnych kart

- Wielokanałowy odczyt

- Deterministyczne sterowanie znacznikami czasu i operacje real-time (na poziomie kilku mikrosekund)

- Wsparcie eksperckie zespołu Creotech Quantum

Zastosowanie

- Sterowanie i kontrola procesorów kwantowych na pułapkach jonowych i zimnych atomach

- Metrologia kwantowa

- Detekcja kwantowa

- Logika kwantowa

Dla kogo?

- Uniwersytety i instytucje badawcze

- Firmy opracowujące komputery kwantowe

- Laboratoria wojskowe (np. do nawigacji bez GPS)

- Koncerny technologiczne

Co zawiera Sinara?

Szeroki wachlarz modułów w formatach Eurocard i MTCA pozwala na kontrolowanie wszystkich aspektów przygotowania kubitów, operacji na nich i ich odczytu. Znalazły się w nim:

- Kontroler FPGA z dystrybucją czasu na pozostałe urządzenia w systemie DAC i ADC – przetworniki cyfrowo-analogowe i analogowo-cyfrowe

- DDS – synteza cyfrowa, generowanie sygnału RF od 0-400 MHz TTL – cyfrowe wejścia/wyjścia

- AWG – generowanie sygnału RF o dowolnym kształcie do 14 GHz

- Wzmacniacze – dedykowane dla sygnału RF oraz wzmacniacze dedykowane dla DAC

- Pętle sprzężenia zwrotnego / Servo – modulowanie lasera, technika PDH

- Stabilizatory – pola magnetycznego i temperatury

- Frame Grabber – wsparcie dla kamer sCMOS/ CCD do odczytu obrazu

Moduły

Kasli SOC

Device Type: Zynq® XC7Z030 SoC (FPGA + ARM CPU)

RAM: 1 GB DDR3

Processor: Yes (via SoC architecture – integrated CPU + FPGA)

Ethernet Connectivity: 1 × RJ45 100/1000T + 4 × SFP

USB: USB 2.0 (UART, JTAG)

EEM Connectors: 12

Reference Clock: 4 × MMCX, 1 × SMA

Application: Advanced controller – operation of Sinara modules via ARTIQ, enabling complex systems combining CPU and FPGA

Power Supply: +12 V (barrel connector, passed through to EEM)

Kasli v2

Device Type: Artix-7 100T FPGA

RAM: 512 MB DDR3

Processor: No CPU – FPGA only

Ethernet / Optical Connectivity: 3 × SFP (Ethernet / DRTIO)

USB: micro-USB (JTAG, debug, flash)

EEM Connectors: 12

Reference Clock: 4 × MMCX, 1 × SMA

Application: Cost-efficient controller / satellite node in a DRTIO network, FPGA-based control of EEM modules

Power Supply: +12 V (barrel connector, same as Kasli-SOC)

DIO SMA

Channels: 8 I/O (2 banks × 4 channels)

Signal Type: TTL

Connectors: SMA

Direction Control: Per bank (4 channels) via onboard switches or I²C

Termination: Optional passive resistor per channel (anti-reflection)

Output Capability: >2.1 V into 50 Ω load

Output Impedance: 50 Ω

Short-Circuit Protection: Unlimited tolerance

Minimum Pulse Width: 5 ns

Max Switching Frequency: 150 MHz (50% load)

Isolation: Separate isolated ground per bank

Additional Features: LED indicators, selectable termination

Panel Width: 8 HP

DIO BNC

Channels: 8 I/O (2 banks × 4 channels)

Signal Type: TTL

Connectors: BNC

Direction Control: Per bank (4 channels) via onboard switches or I²C

Termination: Optional passive resistor per channel (anti-reflection)

Output Capability: >2.1 V into 50 Ω load

Output Impedance: 50 Ω

Short-Circuit Protection: Unlimited tolerance

Minimum Pulse Width: 5 ns

Max Switching Frequency: 150 MHz (50% load)

Isolation: Separate isolated ground per bank

Additional Features: LED indicators, selectable termination

Panel Width: 8 HP

DIO MCX

Channels: 16 I/O

Signal Type: TTL

Connectors: MCX

Direction Control: 4 channel groups via DIP switch, status via I²C and LED

Termination: Optional 50 Ω termination per channel

Output Capability: 50 Ω capable

Output Impedance: 50 Ω

Isolation: Non-isolated

EEM Connectivity: 2 × EEM connectors (single possible)

Additional Features: LED indicators, compact connectors

DIO RJ45

Channels: Up to 16 LVDS I/O (8 with single EEM)

Signal Type: LVDS

Connectors: RJ45

Direction Control: Per signal via I²C or onboard switches

Termination: 100 Ω differential termination (LVDS)

Output Capability: LVDS differential outputs

Output Impedance: 100 Ω differential

Short-Circuit Protection: Short-circuit protected

Max Switching Frequency: 150 MHz tested (higher possible)

Isolation: Non-isolated

EEM Connectivity: Up to 2 × EEM connectors

Additional Features: SPI-compatible LVDS mapping (optional use)

Urukul AD9910

Main function: DDS RF generator

Frequency range: up to ~400 MHz

Channels: 4 DDS

Frequency resolution: ~0.25 Hz (32-bit)

Phase resolution: 16 bit

Amplitude control: 14-bit digital

Update time: 4 ns

RF outputs: 4 SMA

RF chain features: attenuator + RF switch

Key chips: AD9910 DDS

FPGA: controlled by core device

Typical role: dynamic RF control

Urukul AD9912

Main function: High-precision DDS RF generator

Frequency range: up to ~400 MHz

Channels: 4 DDS

Frequency resolution: ~8 µHz (47-bit)

Phase resolution: 14 bit

Amplitude control: none

Update time: 4 ns

RF outputs: 4 SMA

RF chain features: attenuator + RF switch

Key chips: AD9912 DDS

FPGA: controlled by core device

Typical role: ultra-precise RF generation

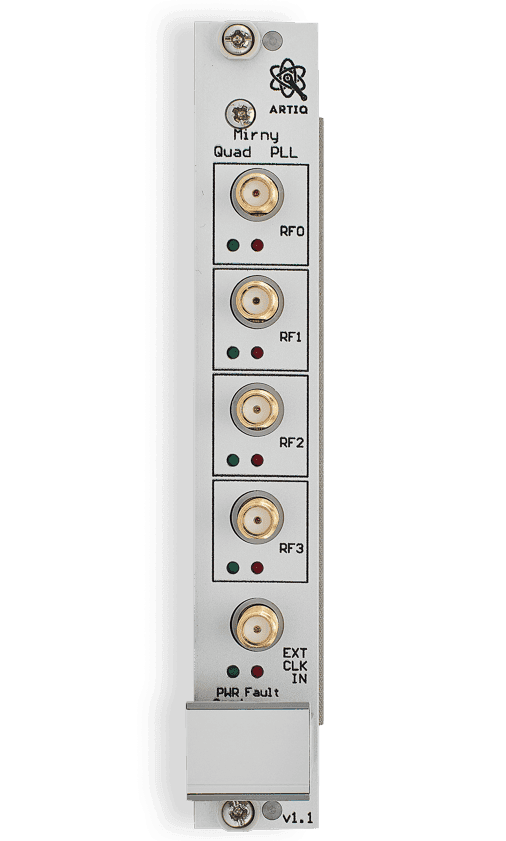

Mirny / Almazny

Main function: Microwave frequency synthesizer

Frequency range: 50 MHz – 4 GHz (up to 12 GHz with Almazny)

Channels typically: 4 PLL channels

Frequency resolution: PLL step dependent

Phase resolution: PLL controlled

Amplitude control: digital attenuation

Update time: slower (PLL tuning)

RF outputs: RF outputs with switches

RF chain features: attenuator, RF switch, amplifiers, filters

Key chips: ADF4355/4356/5355/5356 PLL

FPGA: CPLD routing

Typical role: microwave LO / high-frequency source

Phaser

Main function: Wideband RF signal generator / IQ system

Frequency range: 0.3 – 4.8 GHz (via mixer/VCO)

Channels: 4 RF channels

Frequency resolution: determined by DDS in FPGA

Phase resolution: digital IQ control

Amplitude control: digital attenuator

Update time: deterministic FPGA pipeline

RF outputs: RF outputs via mixers

RF chain features: digital upconversion, IQ mixing

Key chips: FPGA + high-speed DACs

FPGA: Artix-7 FPGA

Typical role: multi-tone RF synthesis

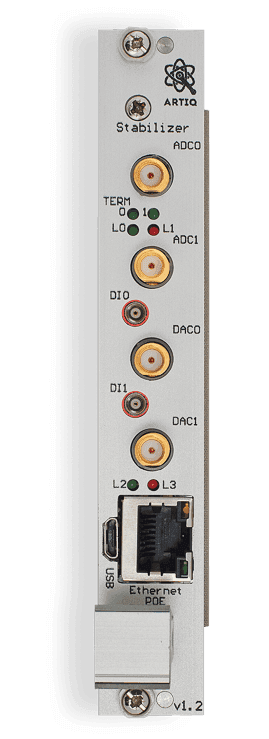

Stabilizer

Main function: Digital feedback controller

Frequency range: depends on connected AFE

Channels: multiple analog IO

Frequency resolution: not a synthesizer

Amplitude control: DAC outputs

Update time: depends on control loop

RF outputs: analog outputs

RF chain features: analog front-end capable

Key chips: STM32H7 + ADC/DAC

FPGA: none (MCU based)

Typical role: feedback control loops

Pounder

Main function: PDH lock RF generator

Frequency range: 1 – 200 MHz

Channels: 4 DDS (AD9959)

Frequency resolution: DDS based

Phase resolution: DDS phase control

Amplitude control: DDS amplitude

Update time: DDS timing

RF outputs: RF outputs

RF chain features: optimized for PDH locking

Key chips: AD9959 DDS

FPGA: relies on Stabilizer

Typical role: Pound-Drever-Hall locking

Fastino

Channels: 32

Resolution: 16-bit

Update Rate: 2.55 MS/s simultaneous, ~1 µs DAC masking

DAC: AD5542ABCPZ, 1 μs settling time

Interface: Dual EEM, 1 Gb/s LVDS, channel masking for reduced crosstalk

Modularity / Connectivity: Lower, optimized for ARTIQ integration

Best Use Case: Maximum simultaneous speed, tight RTIO integration

Zotino

Channels: 32

Resolution: 16-bit

Update Rate: 1 MS/s, arbitrarily divided among channels

DAC: AD5372BCPZ, ±10 V output, 470 Ω + 2.2 nF output impedance

Interface: Single EEM (power + data), HD68/IDC front panel connectors, breakout to BNC/SMA

Power / Thermal: 3 W no load, 8.7 W max load; DAC/reference temperature stabilizable via thermostat

Modularity / Connectivity: High, flexible breakout options for different experimental setups

Best Use Case: Higher output voltage, thermal stability, easy connection to external devices

Sampler BNC

Connector Type: BNC, bayonet (insert + ¼ turn), robust, widely used in labs

Connector Size: Larger, diameter ~14 mm

Impedance / Bandwidth: 50 Ω or 75 Ω, typical bandwidth up to ~4 GHz

Durability: ~500–1000 cycles, solid and robust

Channels: 8

Resolution: 16-bit

Update Rate: Simultaneous 1.5 MS/s per channel

Input Range: ±10 mV to ±10 V

Typical Use: ADC measurements, laser power stabilization, servo with Urukul, lab instrumentation

Mechanical Notes: Bayonet ensures strong mechanical connection, ideal for frequent plug/unplug

Applications: Lab setups, oscilloscopes, analog/digital signals, robust connections

Sampler MCX

Connector Type: MCX, snap-on (press & click), compact, quick to connect

Connector Size: Small, diameter ~3 mm, space-saving

Impedance / Frequency: 50 Ω, typical bandwidth up to ~6 GHz, supports higher frequencies in compact form

Durability / Mating Cycles: ~500 cycles, more delicate

Channel Count: 8

Resolution: 16-bit

Sampling Rate Simultaneous: 1.5 MS/s per channel

Programmable Input Range: ±10 mV to ±10 V

Applications: ADC measurements, laser power stabilization, servo with Urukul, miniaturized devices, RF modules, compact systems

Mechanical Notes: Snap-on is fast to install, but less robust under cable stress

Best Use Case: Space-limited modules, RF/telecom/GPS devices, compact experimental setups

Grabber

Main Function: Interface for scientific cameras (EMCCD/CCD) using Camera Link™

Typical Use Case: Image acquisition from scientific cameras

Supported Devices: Scientific cameras such as Andor iXon Ultra, Life EMCCD 888/897, Andor X3

Interface / Connectors: Camera Link™ Base, Medium, Full → EEM

Signal Type: Camera data stream

Frequency / Speed: Depends on Camera Link configuration

Processing Location: Image processed in Kasli FPGA system

ARTIQ Support: Base and Medium Camera Link configurations supported

Form Factor: EEM module

Power: Via EEM

Special Features: Enables high-speed camera integration with ARTIQ

Connector Options: Camera Link™

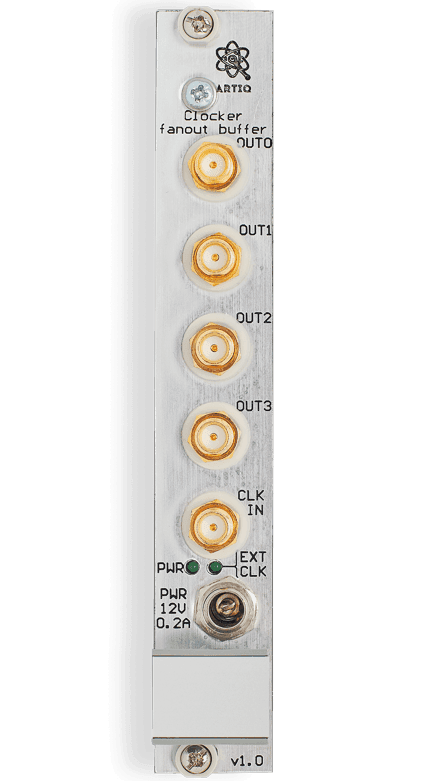

Clocker

Main Function: Distributes a low-jitter clock signal to multiple EEM devices

Typical Use Case: Precise clock distribution and synchronization in experiments

Supported Devices: Any modules requiring a stable reference clock

Interface / Connectors: Inputs: 2 (SMA, MMCX) Outputs: 10 (4 SMA, 6 MMCX)

Signal Type: Clock / timing signal

Frequency / Speed: Up to 1 GHz

Processing Location: Signal distribution only

ARTIQ Support: Used as clock infrastructure within ARTIQ setups

Form Factor: 3U EEM module

Power: 12 V from EEM or front-panel DC jack

Special Features: Low jitter <100 fs RMS; hybrid ground strategy to avoid ground loops

Connector Options: SMA and MMCX

Adapters (SMA_IDC / BNC_IDC / MCX_BNC)

Main Function: Breakout adapters that route IDC connectors to standard RF connectors

Typical Use Case: Connecting DAC/ADC modules (Zotino, Fastino, Banker, Stabilizer) to external equipment

Supported Devices: Zotino, Fastino, Banker, Stabilizer modules

Interface / Connectors: Converts IDC26 connectors to SMA or BNC connectors

Signal Type: Analog or digital signal breakout

Frequency / Speed: Depends on connected module

Processing Location: Passive routing adapter

ARTIQ Support: Used with ARTIQ DAC/ADC modules

Form Factor: Front-panel adapters (4HP or 8HP)

Power: Passive (no power required)

Special Features: Allows flexible connector types and panel density

Connector Options: SMA-IDC (8 SMA), BNC-IDC (8 BNC), MCX-BNC adapter option

Panel Space: BNC version: 8HP panel; MCX version: 4HP panel (more compact)

Power Supply (200W Power Module)

Form factor: 4" × 2" compact PCB design

Output power: 140W (convection), 200W (forced air cooling)

Input voltage range: 80–264 VAC

Output voltage options: 12V to 48V

Efficiency: Up to 95%

No-load power consumption: < 0.5 W

Leakage current: < 130 μA

Cooling:

Convection cooling or forced air, Integrated fan supply: 12V / 0.5A

Protections: Short circuit, Overload, Overvoltage, Overtemperature

Lifetime (MTBF): > 65,000 hours

Operating altitude: Up to 5000 m

Cassing

Opis wkrótce

Cables

Opis wkrótce

Oprogramowanie ARTIQ

ARTIQ (Advanced Real-Time Infrastructure for Quantum physics, z ang. zaawansowana infrastruktura czasu rzeczywistego dla fizyki kwantowej) to nowoczesny system kontroli eksperymentów informatyki kwantowej, opracowany we współpracy ze stale rosnącą grupą instytucji badawczych z całego świata. System posiada język programowania wysokiego poziomu (Python), który pomaga opisywać złożone eksperymenty, jest kompilowany i wykonywany na specjalistycznym sprzęcie z nanosekundową rozdzielczością czasową i opóźnieniem na poziomie poniżej jednej mikrosekundy.

Międzynarodowa społeczność systemu Sinara

Większość sprzętu została zaprojektowana przez Politechnikę Warszawską, przy czym znacząca cześć prac rozwojowych i testów przeprowadzona została przez Creotech Quantum. Integracja z ARTIQ realizowana jest przez M-Labs i QUARTIQ. Prace rozwojowe finansowane są m.in. przez NCBR, Laboratorium Badawcze Armii Stanów Zjednoczonych (United States Army Research Laboratory, ARL), Uniwersytet Duke’a, Uniwersytet Oksfordzki, Uniwersytet Oregonu i Uniwersytet Albrechta i Ludwika we Fryburgu. Urządzenia peryferyjne kompatybilne z modułami Sinara są dostarczane przez partnerów międzynarodowych, m.in. M-Labs, ARL, Uniwersytet Oksfordzki, Uniwersytet Marylandu i Narodowy Instytut Standaryzacji i Technologii w Boulder. Wszystkie prace są licencjonowane zgodnie z warunkami licencji CERN OHL v1.2.

Ekosystem Sinara

FAQ

Większość modułów jest dostępna od ręki. W przypadku zintegrowanych systemów termin ustalany jest indywidualnie, ale zazwyczaj nie przekracza kilku tygodni.

Tak. Zapewniamy customową kalibrację, dopasowaną do konkretnych wymagań eksperymentu lub systemu.

Tak. Moduły są projektowane tak, aby szybko i sprawnie integrowały się z typowymi setupami laboratoryjnymi i istniejącą infrastrukturą.

Tak. Wspieramy klientów na każdym etapie — od doboru modułów, przez integrację, aż po uruchomienie systemu.

Tak. Wszystkie nasze produkty objęte są 1-roczną gwarancją na hardware.